半導体のトランジスタのサイズが小さくなり、チップの複雑さが飛躍的に増す中、高品質の製品だけを市場に送り出すために、セミコンダクタテストは不可欠なものとなっています。 より厳格な許容品質レベル(AQL)認証の導入に伴い、テスト方法はこれらの基準を満たすために常に進化する必要があります。システムレベルテスト(SLT)と自動テスト装置(ATE)を使用した従来のテストは、デバイスが品質要件を上回ることを保証する包括的なテスト戦略を提供します。

多くのテスト問題を特定し、解決することができるシステムレベルテスト(SLT)は、決して新しい技術ではありません。 それは、1990年代後半からコンピューティングの分野で使用されています。 しかし、チップに集積されるトランジスタの飛躍的な増加に伴い、チップの複雑さが増しており、チップの歩留まりと品質を向上させるためにSLTを利用する統合チップ(IC)メーカーが増えています。

システムレベルテストとは何か、他のテストと何が違うのか?

システムレベルテストは、機能テストとも呼ばれ、被テストデバイス(DUT)を最終的に使用する際にテストする方法です。 オペレーティングシステムを実行し、被テストデバイスを使用して一般的またはターゲットとなるアプリケーションテストを行うことで、従来のATEテストとは異なる追加の検証を実現することができます。 SLTテストは、通常、デバイスの通常動作に追加の検証ステップを加えたものです。

システムレベルテストを推進する業界動向

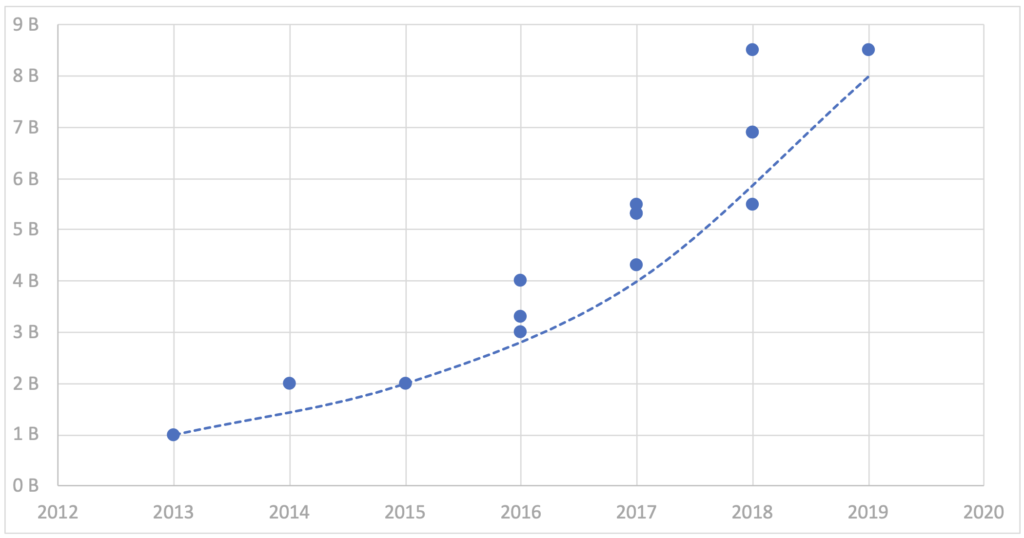

過去20年間、チップ業界のいくつかのトレンドにより、SLT市場は大きく成長しました。

まず、デバイスの品質要求が高まっていることです。 この10年で携帯電話などの電子機器への依存度が高まり、その結果、チップの品質に対する要求もますます高くなっています。 そのため、メーカーは、製品購入後にエンドユーザーが遭遇する問題の可能性を減らすために、チップやシステムの包括的なテストを実施するようになりました。 そのため、モバイル端末向けのSLTが急成長しています。

もう一つのトレンドは、自動車 分野です。アシスト型自律走行車では、電子機器やソフトウェアが事象を感知し、自動操舵や自動ブレーキで対応します。 先進運転支援システム(ADAS)は、より高い規格が求められるため、超高出力デバイスやミックスドシグナルデバイスの性能はもちろん、プラットフォームの効率や熱安定性も重要です。

チップサプライヤーは、性能、バッテリー駆動時間、歩留まりを向上させるために、技術を限界まで追い込み続けています。つまり、サプライヤーは次を実施しなければなりません:

- プロセス障害率が高い場合でも、新しいプロセスノードからできるだけ早く製品を提供する

- できるだけ低い電圧で動作させ、バッテリー駆動時間を長くする

- フェーズロックループ(PLL)の設定を微調整して歩留まりを最大化する

- 最先端のパッケージング技術を採用し、トランジスタの高密度化と高性能化を実現する

さらに、自動車用インフォテインメント分野では、自動車メーカーがこれまで以上にテクノロジーの最前線に接近しています。 最先端の技術を導入し、より高い安定性を実現することで、車載インフォテインメント製品の市場投入までの時間を短縮することができます。

SLTのもう一つの成長分野は、ビッグデータ処理、エッジやクラウドの人工知能(AI)アプリケーションで、数百から数千ワットという高い電力が要求されるものです。

このような多様な市場を牽引するさまざまな要件から、高品質な部品を完成品として出荷することは、重要であると同時に非常に複雑になっています。 技術の限界に挑戦し続ける中で、SLTの活用は、欠陥の見逃しを防ぎ、部品が要求される品質レベルに達することを確実にするために、ますます重要になってきています。 製品の品質向上だけでなく、できるだけ端末のアプリケーションに近い状態で装置を動かすことで、市場投入までの時間を短縮することができます。

従来のテストカバレッジはより厳しくなる

ICメーカーは、より多くの機能を1つのチップに集積することを常に考えています。 モバイルプロセッサーを例に挙げます。 初期のころは、機能は主に電話での通話に限られていました。 現在、モバイルデバイスは、グラフィックス、画像処理、高度なセキュリティなどをサポートしています。 かつてはデジタル処理で通信を実現していましたが、現在のデバイスは音声や生体データの処理、さらにはAIのアルゴリズムも搭載しています。 そのため、アプリケーションプロセッサ(AP)は高速メモリと一体化する必要があります。

プロセッサは時代とともに進化し、提供する機能も急速に拡大しています。 健康指標の追跡、記録と保存、接続と制御、安全を確保するための周辺カーセンサとの通信、機械学習とAIによる人々の生活の簡素化などの機能が、生産性と安全性を常に高めています。 これらの機能ブロックの相互作用に関連する不具合は、特にその中のテストインターフェイスが異なる言語を使用している場合、捕捉が困難となる場合があります。

これらの新しい機能はすべて1つのAPに統合されるため、トランジスタ数が増加し、場合によってはムーアの法則を上回ることになります。

もちろん、テストの課題はデバイスの機能だけにとどまりません。 ICに複数のトランジスタを集積する場合、トレードオフをしなければならないことがあり、従来の方法で達成されたテストカバレッジが失われることになります。 このようにトランジスタ数が増えると、故障が発生する確率が高くなり、故障率の上昇を避けるために追加のテストが必要になります。 ATEテストですべての不具合を検出することはもはや不可能であるため、SLTを使用することで、より包括的なテストカバレッジを達成することができます。

SLTを実行するには?

SLTは、製品の最終用途に近い形で機能テストを行うものです。「システム」部分はカスタムシステムレベル・テストボードに実装され、テストフローは以下の通りです:

- 特定の操作を行う: デバイスの一般的な機能およびシステムに内在するターゲットアプリケーションを実行し、期待通りに動作することを確認します。 操作は、チップの起動、OSのロード、性能評価プログラムなどモジュールが書き込んだ特定のプログラムの実行などを含みます。 使用するシステムレベル・テストボードは、お客様に提供するリファレンスデザインまたは評価ボードと同様のものを使用します。

- 操作が成功したかどうかを判断する: テスト結果や操作の成功/失敗に応じて測定されます。 例えば、内部処理が正常に実行されているかどうかを検証する場合、OSが正常に起動できるかどうかを検証したり、特定の値を測定(例えば、性能テスト結果と閾値を比較)して判断の根拠としたりすることができます。

SLTのシステムには、テストフローを実行するためのオンボードプロセッサが搭載されている場合がほとんどです。SLTは主にSoC(System on a Chip)やSiP(System in Package)チップを対象とするため、テストプロセッサは通常、被テストデバイスの一部となります。 そうでない場合は、被テストデバイスの周辺テストシステムに適切なプロセッサを搭載する必要があります。

被テストデバイス周辺のSLTボード回路は、要件に応じて変更する場合があります。 故障解消報告書は素早く簡単に画面に表示することができます。 この種のテストは、機能障害をトランジスタレベルまで追跡するために、かなりの量の故障解析を行う必要があるため、ATEでは実現が困難です。 SLTがこの種のテストに適しているのは、障害を誘発する正確なユースケースを使用し、この機能テストをSLTテストに素早く追加することで、故障解消の根本原因をほぼ即座に特定できるためです。

しかし、SLTはATEで見られるような構造的なテストではなく、実際の端末の使用シナリオをシミュレートする機能的なテストであるため、SLTのテスト時間は従来のATEよりも長くなるのが一般的です。 そのため、SLTの費用対効果を維持するためには、並行テストの効率化が重要になります。 ATE試験時間は通常10秒単位、SLT試験時間は1~10分単位を基準としています。 最高の効率を実現するためには、並列テストはATEより桁違いに高い必要があります。

コストに関する事項

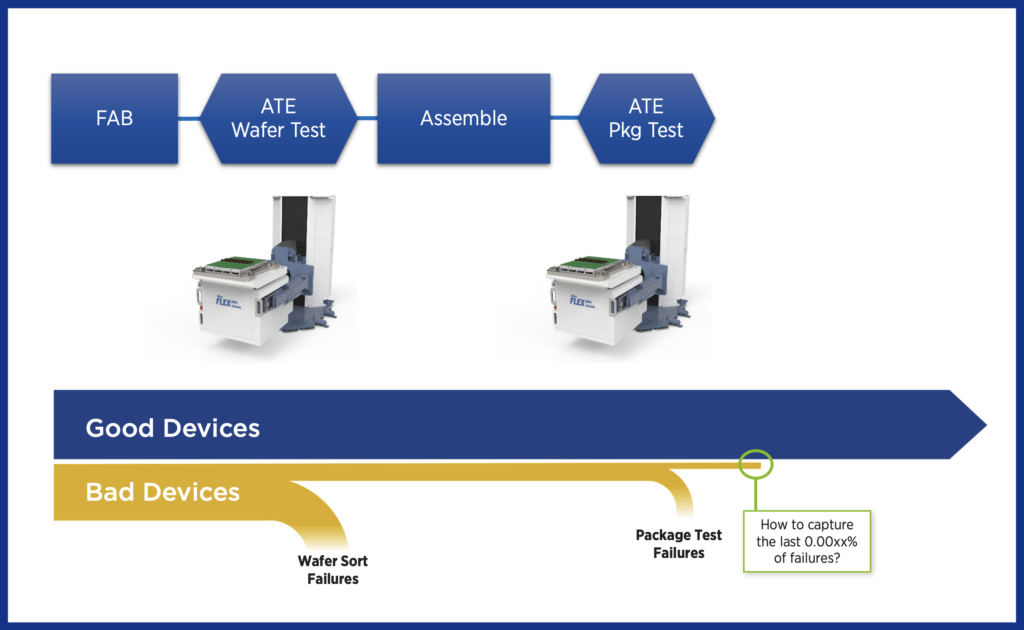

最終的には、コストが重要です。 包括的なテスト戦略により、欠陥を可能な限り早期に捕捉し、下流工程のコスト発生を回避することができます。 ATEウエハーテストは、トランジスタレベルの問題、周波数/電圧レベルの変化に対する感度、基本的な設計仕様への準拠など、プロセスの初期段階で不具合を捕捉するのに適しています。

パッケージング工程で発生する不具合もあり、ATEによるファイナルテストにより、その不具合を特定します。 しかし、低いDPPM(Defective Parts Per million)レベルが要求される場合、デバイスがテスト承認プロセスを通過することができないほど微妙で複雑な欠陥が存在し続けることがあります。

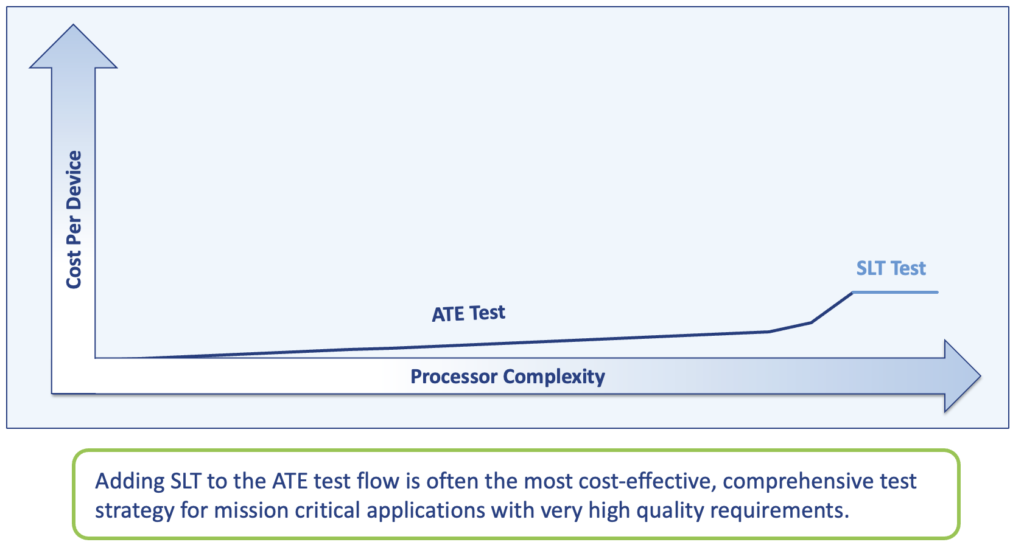

従来の品質要求では、テスト時間が長くなるにつれてATEコストが高くなるのが一般的でした。 この増加は、一般的に制御可能であり、ある程度は直線的です。 しかし、複雑なトランジスタが必要な場合、ATEにかかるコストはやがて曲線の変曲点に達し、指数関数的に増大することになります。

これは主に、これらの故障を特定するのに時間がかかることや、周辺機器でのテストが必要なためです。 一部のパラメータテストや機能テストなど、現在ではATEで完結するものもあります。 しかし、余分な回路の数やテストの長さから、このタイプのテストがATEで実行できないケースもあります。 興味深いのは、SLTのコストおよびテスト時間は、行われるのがアプリケーションの起動や実行だけなので、複雑化しても増加しないことです。 過去50年間、ATEはトランジスタレベルの設計パラメータの不具合を把握するのに非常に優れた方法であり、今後も最も費用対効果の高い方法であり続けるでしょう。 SLTは、実際のチップの応用シナリオを用いたATEで実施できないテストに使用する必要があります。

なぜ、多くのクラスの欠点がATEに取り込まれ、SLTには取り込まれないのか? それは、SLTはATEとは異なり、すべてのトランジスタとそのパラメータを系統的にテストするのではなく、デバイス内の実際のアプリケーションのサブセットをテストし、機能的な結果を提供するだけだからです。 考えられるすべてのアプリケーションプログラムを実行し、すべてのトランジスタを励起して故障を発生させることは、ほとんど不可能です。

TSLTの費用対効果は、ATEではテストできない問題や、チップとその周辺の複数のIPモジュールを同時に刺激することで発生する不具合を、SLTで合理的な割合で発見することで実現します。 同時テスト性(一度にテストするデバイスの数)が非常に高いため、各デバイスのテストコストはATEと比較して1/4以下にできる可能性があります。

複雑さが指数関数的に増加し続け、ミッションクリティカルなアプリケーションの数が増え続ける中、ATEとSLTテストを組み合わせることは、最低コストで高い品質レベルを維持するための理想的なソリューションと言えます。

ATEのコストはある程度、複雑さおよびトランジスタ数に直線的に関係するため、ATEはウェハーレベルやICレベルの不具合を捕捉するために使用するべきものです。 SLTは、テストフローの最後にある、見つけにくい不具合をスクリーニングするのに非常に効果的です。 そのため、非常に高い品質が要求されるミッションクリティカルなアプリケーションでは、既存のATEテストフローの最後にSLTを追加することが、しばしば最もコスト効率の良い戦略となります。

テラダインが選ばれる理由

ATEテストとSLTテストの両方を利用してこそ、包括的なテスト戦略を実現することができます。 要求される品質レベルやコストなど、さまざまな要素を考慮することで、企業はATEとSLTの最適なバランスを判断することができます。

テラダインのTeradyne Titan™ SLTテスターの利点のひとつに、真のパラレルテストがあります。 各チップは隣接するチップから完全に独立しているため、SLTやバッチ処理をより効果的に行うことができます。

また、テラダインは10年以上前から大規模な自動生産プラットフォームを保有しています。テラダインのTitanは、弊社のストレージ自動化アーキテクチャとセミコンダクタテストの専門知識を組み合わせることで、包括的なSLT自動化およびテストソリューションを提供します。

SLTは、必要な品質レベルが満たされていることを確認するための補助的なテストステップであり、ATEテストの延長線上にあるものです。 テラダインは、テストライフサイクル全体をサポートするソリューションを提供し、お客様がテスト時間とコストを削減しながら、最高品質の製品を市場に送り出すために最大限のテストカバレッジを達成できるようにします。

結論

SLTは30年近く前から存在し、主に最先端の大規模デジタルコンピューティングアプリケーションに使用されています。 不具合には、実際のアプリケーションのシナリオでしか見ることのできないものもあり、SLTはこれに特化しています。 システムレベルのテストボード上のチップを専用ペリフェラルを使ってアプリケーションレベルでテストするもので、最後の0.00xx%の不具合を捕捉し、可能な限り低いエラー率を達成します。

SLTの成長の背景には、品質に対する要求の高まり、電子機器の応用シーンの急増、チップの複雑化、市場投入までの時間の短縮化などがあります。 テラダインは、ATEとSLTテストを組み合わせることで、最も多くの不具合を捉えることを目的としており、携帯電話のアプリケーションプロセッサだけでなく、自動車やハイパフォーマンスコンピューティングのエンドマーケットのプロセッサにも対応できる、大量生産向けの包括的なテストソリューションを提供しています。

システムレベルテストのホワイトペーパーをご覧ください。

テラダインのSLTおよびATEソリューションの詳細については、弊社までお問い合わせください。

Natalian Z. Derは、テラダインのビジネス戦略およびシステムレベルテストマーケティングのディレクターです。Natalianは2018年にテラダインに入社し、テラダインのUltraFLEXplus製品を管理し、テラダインの中国戦略をリードしています。 テラダイン入社以前は、サムスン傘下のHarmanで、カー・アフターマーケット・エレクトロニクスラインのグローバル・プロダクト・ラインマネジメントのシニアディレクターを務めていました。Natalianはシリコンラボでキャリアをスタートさせ、携帯電話や自動車市場向けの放送用RF ICを管理してきました。Natalianは、テキサス州ヒューストンのライス大学で電気工学の修士号と経営学の修士号を取得しています。